Двухтактные триггеры

К основным недостаткам рассмотренных выше однотактных триггеров следует отнести: срабатывание триггеров по уровню импульса, в результате чего за время тактового импульса, при изменении уровня на информационных входах, триггер меняет свое состояние; наличие аналоговых элементов задержки сильно усложняет схему и накладывает ограничение на её работу (τи < τз в T-триггере).

Исключить эти недостатки позволяют двухтактные триггеры, в которых запоминание информации осуществляется по фронту тактового импульса.

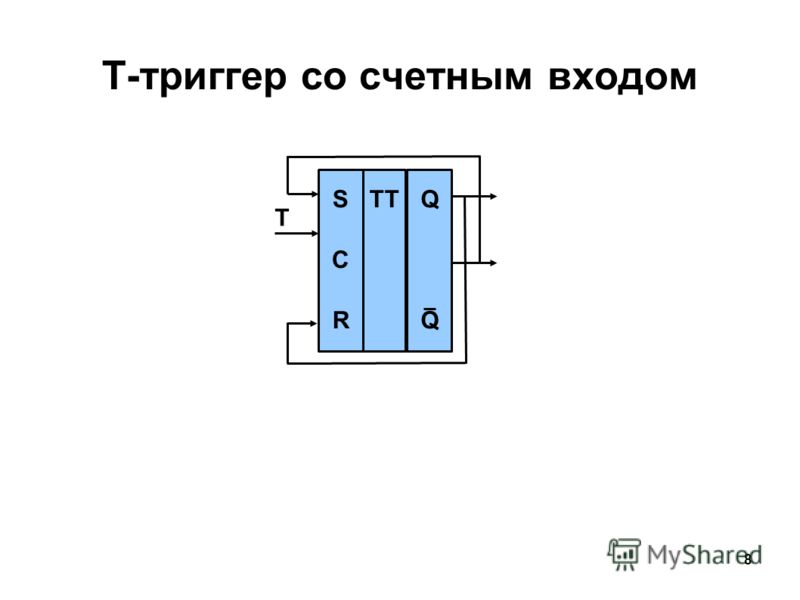

Триггер T-типа. Двухтактные триггеры Т-типа выполняются на базе двух однотактных RS-триггеров, один из которых называют основным (DD2), а другой – вспомогательным (DD1). Особенностью рассматриваемой схемы является наличие в ней дополнительного инвертора (DD3), управляющего вспомогательным триггером DD1.

Рис. | |

Пусть в начальный момент триггер DD2 находится в состоянии 0, (рис. 3.35). Тогда через обратные связи на вход R вспомогательного триггера DD1 действует лог.1, а на вход S – лог.0. Как только на тактовый сигнал T подается лог.1, триггер DD1 сбрасывается (). На вход R основного триггера DD2 начинает действовать лог.0, а на вход S – лог.1. Установка сигнала T в низкое состояние приведет к тому, что через инвертор DD3 на тактовый вход основного триггера DD2 будет действовать лог.1. Это приведет к записи в DD2 лог.1, т.е. триггер переключится в противоположное состояние. Таким образом, каждый задний фронт тактового импульса будет приводить к переключению триггера.

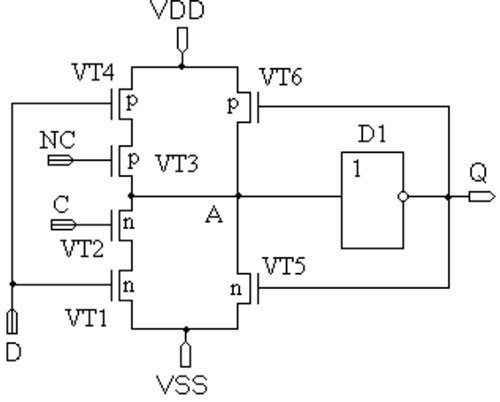

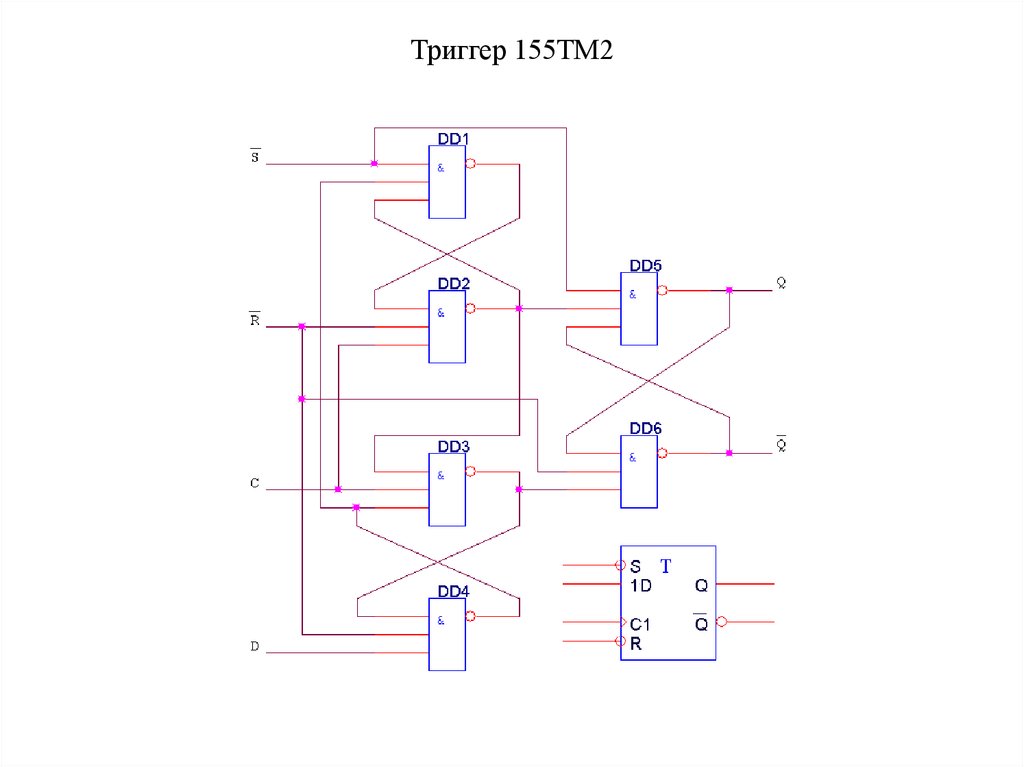

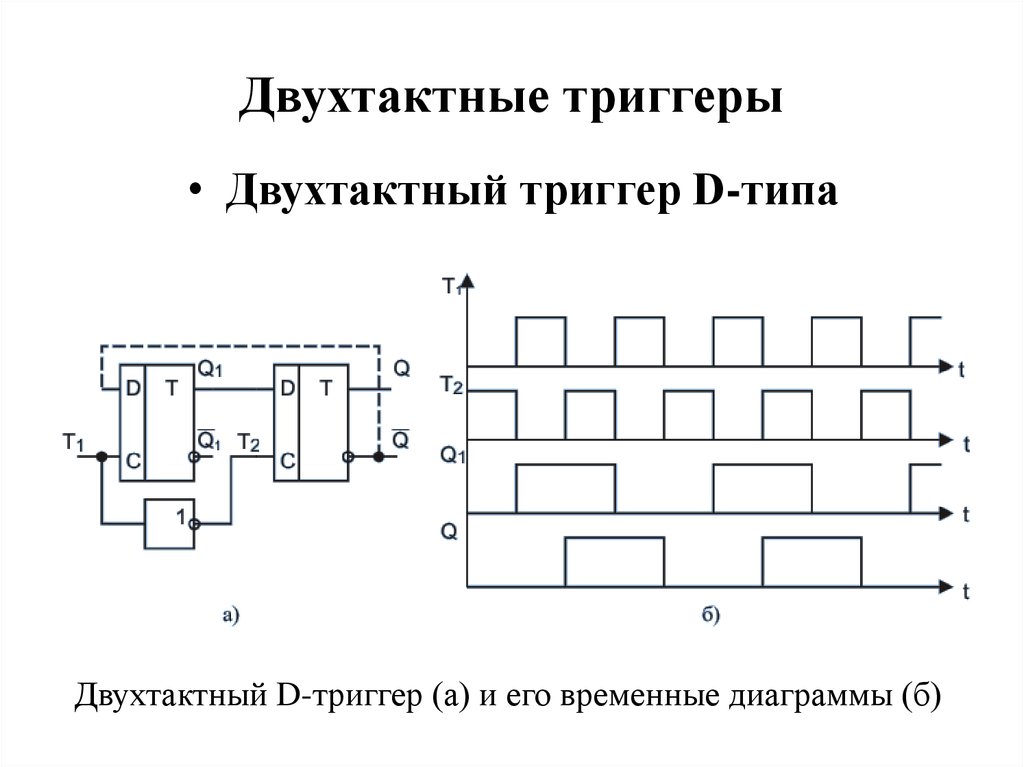

Двухтактный

триггер D-типа. Двухтактные

триггеры D-типа выполняются на базе двух

однотактных D-триггеров, один из которых

называют основным, а другой –

вспомогательным (рис. 3.36). В них

последовательно записывается информация

по двум тактовым импульсам – T1 и T2 .

Пунктиром показана электрическая связь для организации двухтактного счетного триггера.

а) б)

Рис. 3.41. Двухтактный D-триггер (а) и его временные диаграммы (б)

Двухтактные

триггеры могут работать: по

переднему фронту или по заднему фронту.

Тактовые входы таких триггеров на УГО

обозначаются косой чертой (рис. 3.37).

3.37).

Рис. 3.42. D-триггер, срабатывающий по переднему (слева) и по заднему (справа) фронту тактового импульса

Регистрами называются многоразрядные цифровые запоминающие устройства, предназначенные для приёма, хранения, преобразования и передачи информации.

Основу регистра составляют триггеры. Обычно используются D-триггеры, как наиболее удобные для записи и хранения информации. Чаще всего используются двухтактные D-триггеры, в которые запоминание осуществляется по фронту тактового импульса, гораздо реже – RS-триггеры.

Регистры делятся на параллельные, последовательные и параллельно-последовательные.

Рис. 3.43. Параллельный регистр |

Параллельные регистры. Параллельный n-разрядный

регистр представляет собой n триггеров, на информационные входы

которых подается n-разрядный

двоичный код, который необходимо

запомнить, а на объединенные тактовые C-входы

подаётся тактовый импульс, по переднему

фронту которого осуществляется

запоминание (рис. 3.38). В регистре может

быть дополнительный вход R сброса

регистра в нулевое состояние.

Параллельный n-разрядный

регистр представляет собой n триггеров, на информационные входы

которых подается n-разрядный

двоичный код, который необходимо

запомнить, а на объединенные тактовые C-входы

подаётся тактовый импульс, по переднему

фронту которого осуществляется

запоминание (рис. 3.38). В регистре может

быть дополнительный вход R сброса

регистра в нулевое состояние.

Последовательные регистры. Последовательные регистры работают с последовательным кодом, разряды которого разделены во времени на интервалы, равные периоду следования тактового импульса T. Такой способ представления информации широко используется при передаче информации между цифровыми устройствами, что позволяет экономить количество проводов, по которым передаётся информация. Недостатком является значительное время передачи информации.

Различают регистры прямого

сдвига и реверсивные

регистры. Регистры

прямого сдвига осуществляют приём

(передачу) информации, сдвигая её в

регистре на 1 разряд вправо при приходе

одного тактового импульса. Для полного

приёма (передачи) информации требуется n тактов. Регистр представляет собой n последовательно соединённых D-триггеров,

тактовые входы которых объединены.

Имеется один информационный вход I для приёма информации (рис. 3.39). Вход

R позволять сбросить все триггеры

регистра одновременно.

Для полного

приёма (передачи) информации требуется n тактов. Регистр представляет собой n последовательно соединённых D-триггеров,

тактовые входы которых объединены.

Имеется один информационный вход I для приёма информации (рис. 3.39). Вход

R позволять сбросить все триггеры

регистра одновременно.

Реверсивный сдвиговый регистр позволяет осуществить сдвиг информации внутри регистра как вправо, так и влево. Это может потребоваться для преобразования последующего кода. Например, если первоначально следовал старший разряд кода, то после преобразования первым будет преобразован младший разряд кода. Для организации реверсивного режима между входами и выходами триггеров включаются одноразрядные мультиплексоры с двумя информационными входами (рис. 3.40).

Рис. 3.44. Последовательный регистр прямого сдвига

Рис. 3.45. Реверсивный регистр

Вход

V управляет направлением сдвига

информации. При V = 0 к выходу мультиплексора

подключён вход I1 и схема преобразуется

в схему со сдвигом информации вправо.

При V = 1 к входам мультиплексора подключён

вход I2. При этом выход последующего

триггера подключается к информационному

входу предыдущего, и таким образом при

приходе тактовых импульсов осуществляется

сдвиг информации влево.

При V = 0 к выходу мультиплексора

подключён вход I1 и схема преобразуется

в схему со сдвигом информации вправо.

При V = 1 к входам мультиплексора подключён

вход I2. При этом выход последующего

триггера подключается к информационному

входу предыдущего, и таким образом при

приходе тактовых импульсов осуществляется

сдвиг информации влево.

Параллельно-последовательные регистры. Такие регистры служат для преобразования информации с последовательного кода в параллельный или наоборот, а также могут выполнять функции как последовательных, так и параллельных регистров.

Для организации одновременного наличия двух режимов (параллельного и последовательного) чаще пользуются более простым схемотехническим решением – между триггерами включают одноразрядный мультиплексор (рис. 3.41).

Рис. 3.46. Параллельно-последовательный регистр

При

V = 0 организуется режим параллельного

регистра. При этом в мультиплексорах к

выходам подключены входы I1, на которые

подаётся параллельный код.

Рис. 3.47. Параллельно-последовательный реверсивный регистр

Память

Запоминающие

устройства (ЗУ) или память предназначены для запоминания некоторого

количества многоразрядных чисел и

представляют собой такое же количество

линейных регистров. Выбор линейного

регистра осуществляется с помощью

дешифратора, который обычно встроен в

микросхему. Использование встроенных

дешифраторов позволяет значительно

сократить количество выводов микросхемы,

так как для входов и выходов регистра

используются одни и те же выводы

микросхемы, подключаемые к разным

регистрам через цифровые ключи,

управляемые от дешифратора.

Рис. 3.48. Структурная схема запоминающего устройства:

m – количество разрядов каждого числа; n – разрядность адресного кода

Оперативное запоминающее устройство (ОЗУ). ОЗУ используются для многократной перезаписи в них информации. ОЗУ бывают статические и динамические

. Статические строятся на основе триггеров, а в динамических в качестве запоминающих элементов (ЗЭ) используются ёмкости (конденсаторы), подключённые через полевой транзистор к шине данных, чтобы увеличить время разряда.Рис. 3.49. Фрагмент структурной схемы динамического ОЗУ |

Достоинством динамических

ОЗУ является значительное сокращение

транзисторов, используемых для построения

запоминающих элементов. Недостатком

динамических ОЗУ является наличие

ёмкости, которая имеет свойства

разряжаться с течением времени. Этот

недостаток устраняется путём организации

режима регенерации, т.е. восстановления

напряжения на ёмкости через заданный

интервал времени – обычно от 1 до 10 мкс.

Недостатком

динамических ОЗУ является наличие

ёмкости, которая имеет свойства

разряжаться с течением времени. Этот

недостаток устраняется путём организации

режима регенерации, т.е. восстановления

напряжения на ёмкости через заданный

интервал времени – обычно от 1 до 10 мкс.

На

рисунке 3.44, кроме ЗЭ,

упрощенно показаны цепи, необходимые

для пояснения принципов записи-считывания

информации. Запоминающий элемент

включает конденсатор С

К

ШД

подключен затвор транзистора VT2,

выполняющего роль усилителя считывания.

После подключения нужного конденсатора

к ШД

с выхода усилителя снимается напряжение,

пропорциональное исходному напряжению

на конденсаторе СП. ШД

имеет большую собственную емкость СШ.

Как правило, выполняется условие СШ > СП.

Подключение к ШД

конденсатора малой емкости за счет

перераспределения зарядов емкостей СШ и СП незначительно изменяет ее потенциал.

Для распознания этого изменения

необходимо очень точно знать исходное

напряжение шины, которое в процессе

работы может принимать произвольное

значение. Поэтому процесс считывания

информации предполагает следующую

последовательность действий:

ШД

имеет большую собственную емкость СШ.

Как правило, выполняется условие СШ > СП.

Подключение к ШД

конденсатора малой емкости за счет

перераспределения зарядов емкостей СШ и СП незначительно изменяет ее потенциал.

Для распознания этого изменения

необходимо очень точно знать исходное

напряжение шины, которое в процессе

работы может принимать произвольное

значение. Поэтому процесс считывания

информации предполагает следующую

последовательность действий:

– непосредственно перед считыванием информации фиксируют уровень напряжения ШД, для чего при помощи ключа VT3 емкость СШ заряжают до напряжения питания;

– на нужный запоминающий элемент подают сигнал выборки CS; СП подключается к СШ, что сопровождается перераспределением заряда и соответствующим изменением напряжения на ШД;

–

с выхода усилителя считывают сигнал,

пропорциональный заряду конденсатора

выбранного запоминающего элемента.

Считывание информации сопровождается ее разрушением. Запись информации выполняется с использованием транзисторов VT3 и VT4, которые по сигналу управления подключают ШД либо к источнику питания, либо к общей шине. При выборке нужного запоминающего элемента его конденсатор заряжается до напряжения ШД.

Реальная структура ИС динамического ОЗУ много сложнее показанного упрощенного варианта. Она содержит регистры и цепи управления процессами регенерации, а также дополнительную матрицу запоминающих элементов, использующуюся в качестве эталона. Для регенерации по сигналу с блока управления содержимое целой строки матрицы переписывается в регистр и обратно, за счет чего поддерживается требуемый уровень напряжения на конденсаторах памяти.

Постоянные запоминающие

устройства (ПЗУ). ПЗУ

предназначены для длительного хранения

записанной в них информации без

перезаписи. Они

бывают масочные

(информация в них записывается

непосредственно в процессе их

изготовления), с однократным

программированием (обычно путём

прожигания информации) и с многократным

программированием (ультрафиолетовое

или электрическое стирание информации).

Особенностью ПЗУ является отсутствие входов записи информации (программирование или прожигание осуществляется через выходы регистра, а в качестве запоминающих элементов обычно используют диоды или транзисторы в режиме инвертирующего повторителя).

На рисунке 3.45 приведена схема простейшего ПЗУ с организацией 4×8. Она включает дешифратор с двумя адресными шинами, восемь балластных резисторов Rб1-Rб8 выходных шин и диоды, число которых равно числу логических 1, записанных в ПЗУ.

Рис. 3.50. ПЗУ с организацией 4×8

Работа

ПЗУ сводится к следующему. После появления

на выходе дешифратора напряжения

высокого уровня, при наличии связи через

диод между адресной шиной и шиной данных,

это напряжение прикладывается к

соответствующему балластному резистору,

что воспринимается как появление на

шине сигнала логической единицы. При

отсутствии связи ток через соответствующий

резистор не протекает, что классифицируется

как сигнал логического нуля.

а) б) |

Рис. 3.51. Фрагменты масочных ПЗУ на биполярных (а) и полевых (б) транзисторах |

В масочных ПЗУ связь между шиной дешифрованного адреса и шиной данных обеспечивается с помощью транзисторов, у которых могут отсутствовать некоторые части. Отсутствие части транзистора классифицируется как отсутствие связи (рис. 3.46).

В

ПЗУ с однократным программированием

первоначально имеется связь между шиной

дешифрованного адреса и шиной данных

для всех запоминающих элементов. Процесс

записи осуществляется путем разрушения

(пережигания) специально для этого

предусмотренных перемычек между шинами

дешифрированного адреса и выходными

выводами. Такие перемычки изготавливаются

из нихрома, поликремния или титаната

вольфрама и имеют собственное сопротивление

в несколько десятков Ом. Перемычка

обычно включается в эмиттерную цепь

транзистора. При программировании для

разрушения такой перемычки через

транзистор достаточно пропустить

импульс тока в 20…30 мА при длительности

порядка 1мс. В нормальном режиме работы

токи схемы существенно меньше необходимых

для программирования, поэтому записанная

информация при чтении не разрушается.

Перемычка

обычно включается в эмиттерную цепь

транзистора. При программировании для

разрушения такой перемычки через

транзистор достаточно пропустить

импульс тока в 20…30 мА при длительности

порядка 1мс. В нормальном режиме работы

токи схемы существенно меньше необходимых

для программирования, поэтому записанная

информация при чтении не разрушается.

Рис. 3.52. Запоминающий элемент репрограммируемого ПЗУ |

Репрограммируемые ПЗУ по сути являются электростатическими ЗУ. Логика построения их запоминающих элементов подобна логике запоминающих элементов динамического ОЗУ. Отличие состоит в том, что непосредственно носителем информации в них является не конденсатор, а специализированный МДП-транзистор (транзистор с «плавающим» затвором или МДП-транзистор с двухслойным диэлектриком) (рис. 3.47).

Транзистор

VT1 служит для выбора по сигналу с выхода

дешифратора адреса соответствующего

транзистора памяти – VT2. Шина через

ограничительный резистор подключена

к выводу источника питания. При отпирании

транзистора VT1 протекание тока в цепи

его стока зависит от состояния транзистора

VT2. Наличие или отсутствие тока

классифицируется как хранение сигналов

логический 0 или логическая 1. Обычно,

если ток в цепи стока VT2 протекает,

считают, что в ячейке был записан сигнал

логический 0, если ток отсутствует –

сигнал логическая 1.

Шина через

ограничительный резистор подключена

к выводу источника питания. При отпирании

транзистора VT1 протекание тока в цепи

его стока зависит от состояния транзистора

VT2. Наличие или отсутствие тока

классифицируется как хранение сигналов

логический 0 или логическая 1. Обычно,

если ток в цепи стока VT2 протекает,

считают, что в ячейке был записан сигнал

логический 0, если ток отсутствует –

сигнал логическая 1.

Последовательностные системы — триггеры

Последовательностные системы — триггеры| Справочное руководство по Electronics Workbench |

3.3.1 Последовательностные системы — триггеры

Раздел: Цифровая схемотехника

Теоретическое введение:

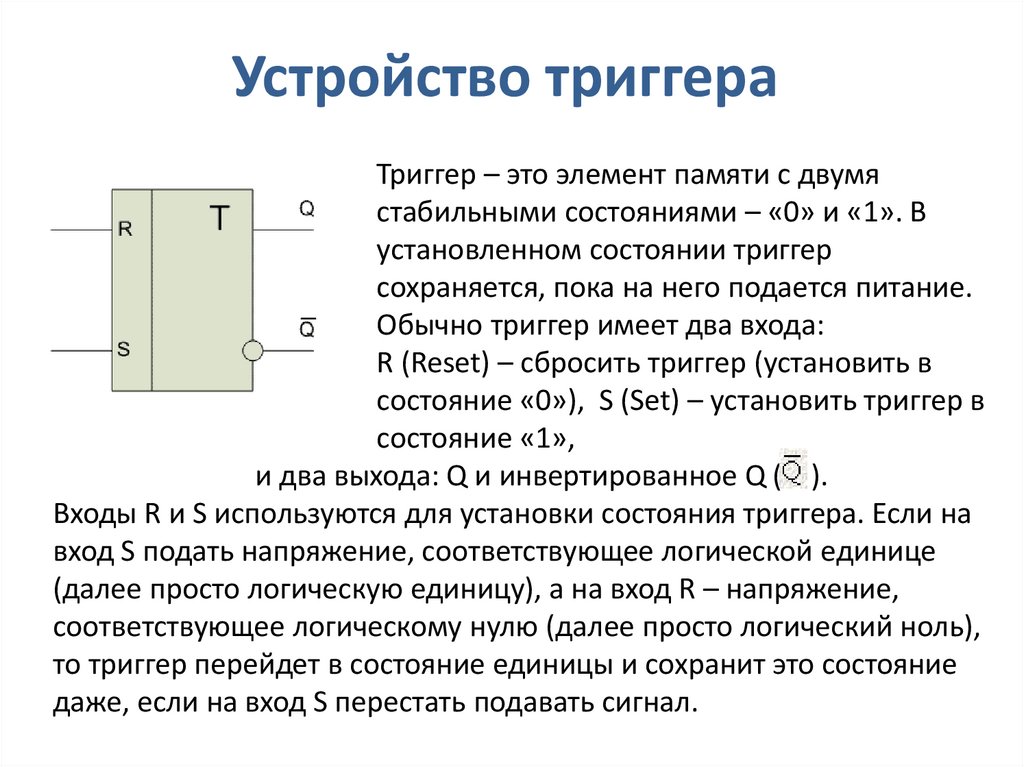

Триггер — цифровой автомат,

имеющий два устойчивых состояния равновесия либо 0, либо 1. на его инверсном

выходе).

на его инверсном

выходе).

Законы функционирования триггеров задаются таблицами переходов с компактной записью, при которой в столбце состояний может быть указано, что новое состояние совпадает с предыдущим либо является его отрицанием

Типы триггеров.

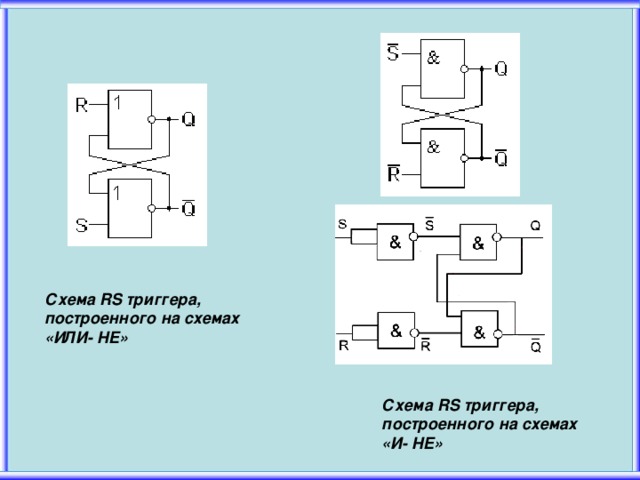

Триггер типа RS имеет два входа раздельной установки в нулевое и единичное состояния. Воздействие по входу S (обозначен по первой букве слова set – установка) приводит триггер в единичное состояние, а воздействие по входу R (от первой буквы слова reset – сброс) – в нулевое. Одновременная подача сигналов S и R не допускается, что является недостатком для RS-триггера.

Асинхронный RS-триггер на

элементах И-НЕ показан на рисунке 3.3.1.1. Триггер

образован из двух комбинационных схем И-НЕ, соединенных таким образом, что

возникают положительные обратные связи, благодаря которым в устойчивом состоянии

выходной транзистор одной схемы ИЛИ-НЕ закрыт, а другой открыт. Таблица 3.1.1.1 определяет закон функционирования триггера. На рисунке 3.3.1.2 приведена временная диаграмма иллюстрирующая

работу асинхронного RS-триггера.

Таблица 3.1.1.1 определяет закон функционирования триггера. На рисунке 3.3.1.2 приведена временная диаграмма иллюстрирующая

работу асинхронного RS-триггера.

Рисунок 3.3.1.1 — Схема асинхронного RS-триггера на элементах И-НЕ

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

0 |

1 |

1 |

Установка 1 |

|

1 |

0 |

0 |

Установка 0 |

|

1 |

1 |

— |

Запрещено |

Таблица 3. 3.1.1 — Таблица переходов асинхронного

RS-триггера на элементах ИЛИ-НЕ

3.1.1 — Таблица переходов асинхронного

RS-триггера на элементах ИЛИ-НЕ

Рисунок 3.3.1.2 — Диаграмма работы асинхронного RS-триггера

При R=1 и S=0 триггер устанавливается в нулевое состояние Q=0; при R=0 и S=1 он устанавливается в единичное состояние Q=1; при R=S=0 триггер сохраняет состояние, в котором он находился до момента поступления на его входы нулевых сигналов. При R=S=1 на прямом и инверсном выходах устанавливается нулевой сигнал. Триггероное кольцо превращается в два независимых инвертора, и при переходе к хранению (R=S=0) триггер может устанавливаться в любое состояние. Поэтому такая комбинация входных сигналов запрещена.

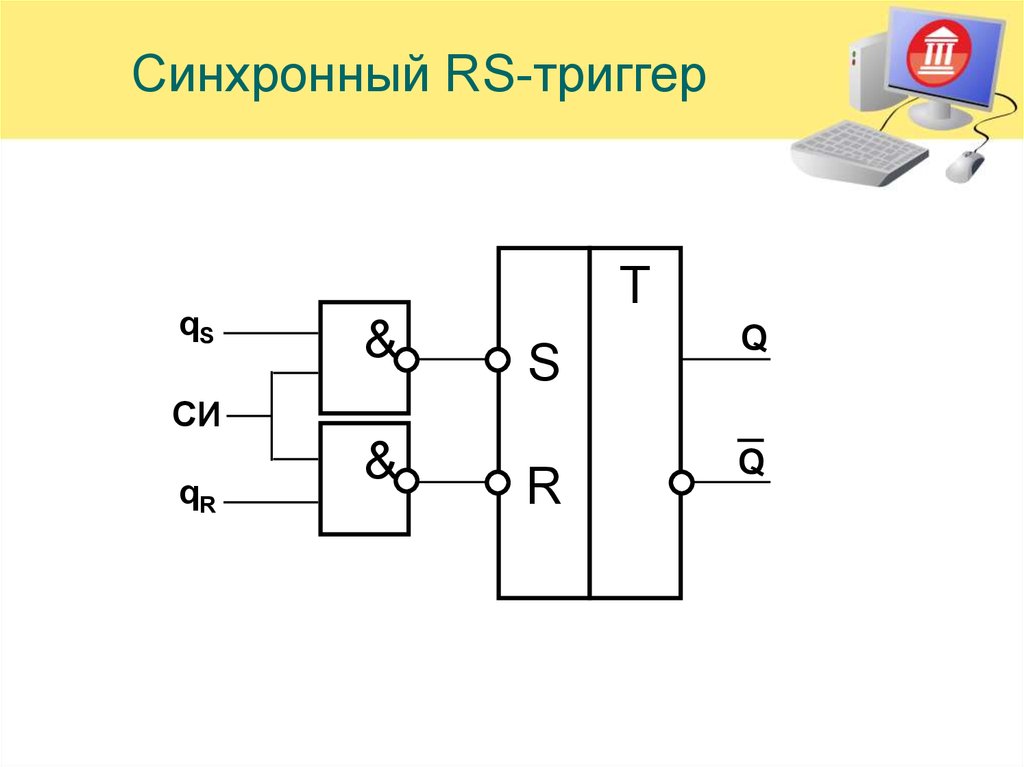

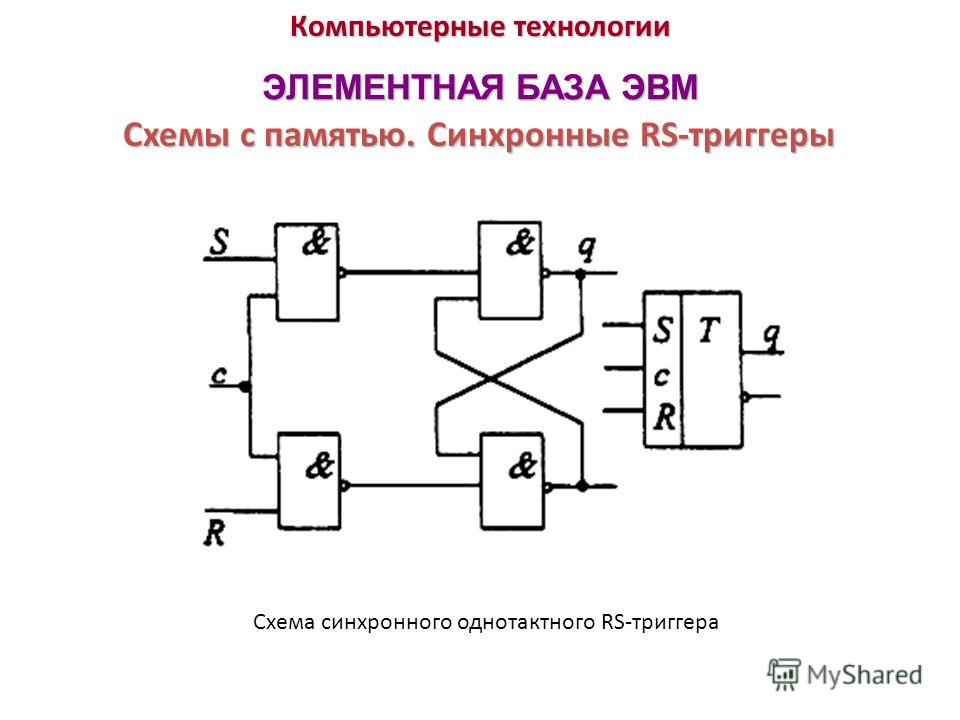

Синхронизируемый однотактный

RS-триггер приведен на рисунке 3.3.1.3. Такие RS-триггеры имеют два

информационных входа R и S и вход синхронизации C. Кроме того, триггер может

иметь несинхронизируемые входы R и S. В этом случае функционирование триггера

осуществляется либо под воздействием несинхронизируемых входов при С=0, либо под

воздействием синхронизируемых входов. В последнем случае на несинхронизируемых

входах должны присутствовать сигналы, которые не влияют на состояние схемы.

На рисунке 3.3.1.4 приведена временная диаграмма

иллюстрирующая работу синхронного однотактного RS-триггера.

В этом случае функционирование триггера

осуществляется либо под воздействием несинхронизируемых входов при С=0, либо под

воздействием синхронизируемых входов. В последнем случае на несинхронизируемых

входах должны присутствовать сигналы, которые не влияют на состояние схемы.

На рисунке 3.3.1.4 приведена временная диаграмма

иллюстрирующая работу синхронного однотактного RS-триггера.

Рисунок 3.3.1.3 — Схема синхронного RS-триггера

Рисунок 3.3.1.4 — Диаграмма работы синхронного RS-триггера

Таблица 3.3.1.2 определяет переходы RS-триггера для синхронизируемых входов R и S. Работа в соответствии с данной таблицей осуществляется при сигнале несинхронизируемого входа R=1 и при С=1.

|

R |

S |

Q |

Примечание |

|

1 |

1 |

Q |

Хранение |

|

1 |

0 |

1 |

Установка 1 |

|

0 |

1 |

0 |

Установка 0 |

|

0 |

0 |

— |

Запрещено |

Таблица 3. 3.1.2 — Таблица

переходов для однотактного RS-триггера

3.1.2 — Таблица

переходов для однотактного RS-триггера

Входная информация заносится в синхронизируемый однотактный RS-триггер через элементы входной логики 1 и 2 в момент поступления сигнала синхронизации С. В отсутствие сигнала синхронизации триггер может быть установлен в состоянии 0 путем подачи на несинхронизируемые вход R сигнала R=0.

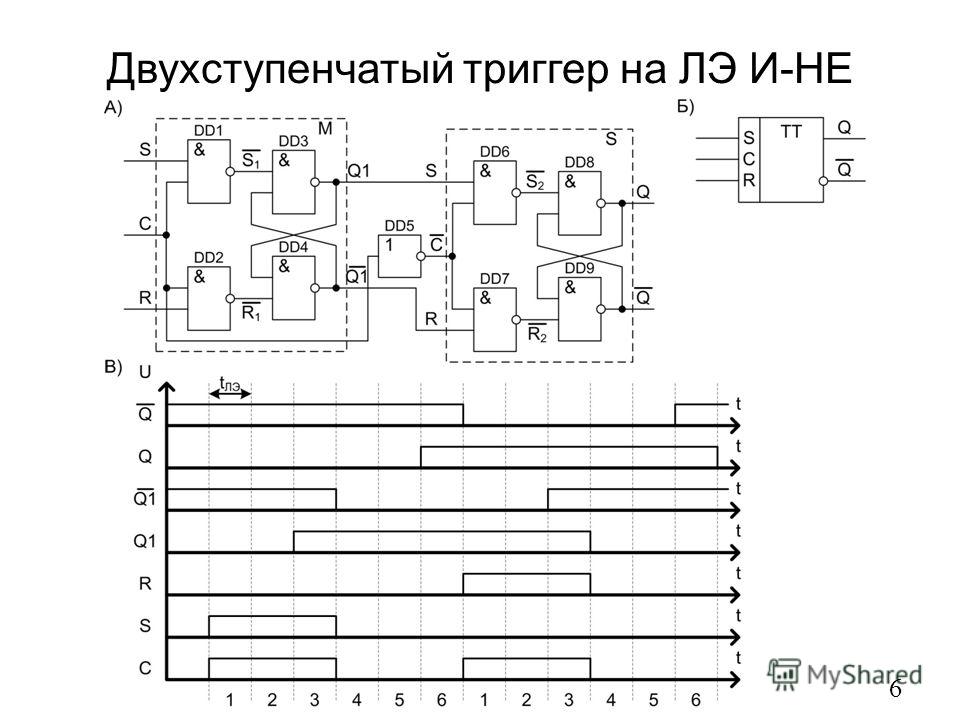

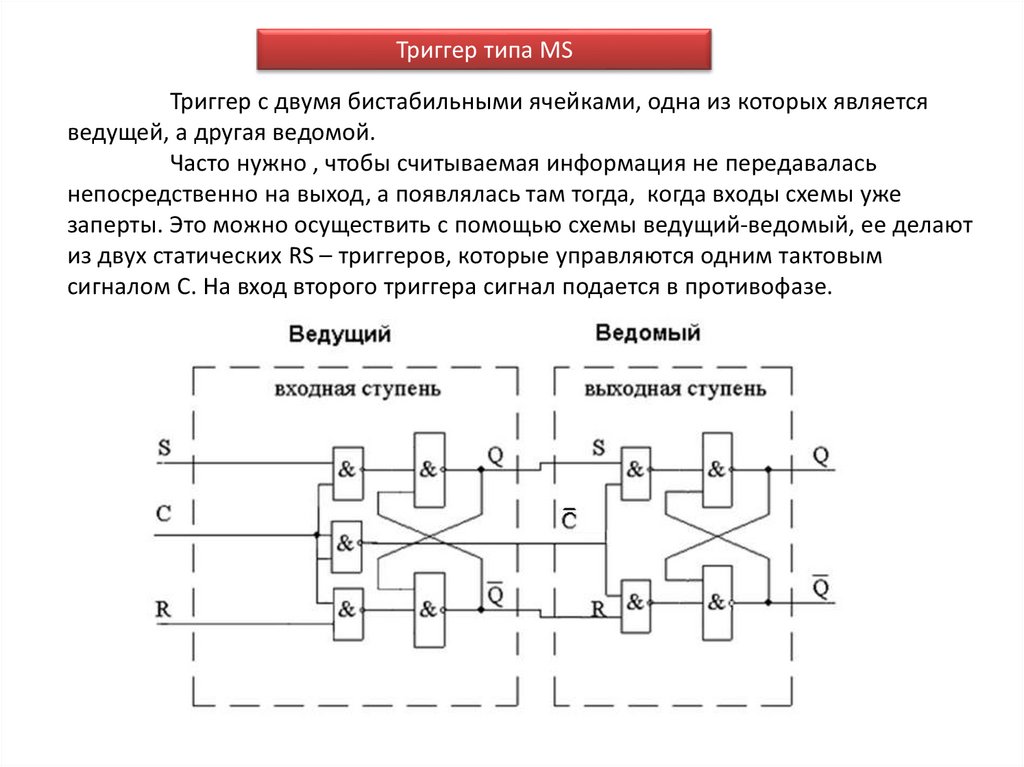

Двухтактный RS-триггер.

Устойчивая работа однотактных RS- триггеров в схеме с передачей информации между

триггерами возможно только в случае, если занесение в триггер информации

осуществляется после завершения передачи информации о прежнем его состоянии в

другой триггер (см. рисунок 3.3.1.5).

Это достаточно просто обеспечивается при использовании двух серий находящихся в

противофазе синхросигналов. Таблица 3.3.1.3 задает закон

функционирования такого двухтактного триггера. Этот тирггер изменяет свои

состояния только после окончания действия сигнала синхронизации С=1 (переход в

режим хранения информации). Поэтому из двухтактных триггеров можно строить

произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

Поэтому из двухтактных триггеров можно строить

произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

|

R |

S |

Q |

Примечание |

|

0 |

0 |

Q |

Хранение |

|

1 |

0 |

0 |

Установка 0 |

|

0 |

1 |

1 |

Установка1 |

|

1 |

1 |

— |

Запрещено |

Таблица 3. =1, первый RS- триггер перейдет в режим хранения,

а второй примет то же состояние, что и первый. В результате к следующему такту

на входе двухтактного RS- триггера появится сигнал нового состояния. На рисунке 3.3.1.6, приведена временная диаграмма иллюстрирующая

работу двухтактного RS-триггера.

=1, первый RS- триггер перейдет в режим хранения,

а второй примет то же состояние, что и первый. В результате к следующему такту

на входе двухтактного RS- триггера появится сигнал нового состояния. На рисунке 3.3.1.6, приведена временная диаграмма иллюстрирующая

работу двухтактного RS-триггера.

Рисунок 3.3.1.6 — Диаграмма работы двухтактного RS-триггера

Проектирование схем в Electronics Workbench

При проектировании схем в Electronics Workbench использовались элементы панели инструментов «Digital» и соответствующие функциональные элементы : Or, Nor, And, Nand.

Рисунок 3.3.1.7 — Панель инструментов «Digital»

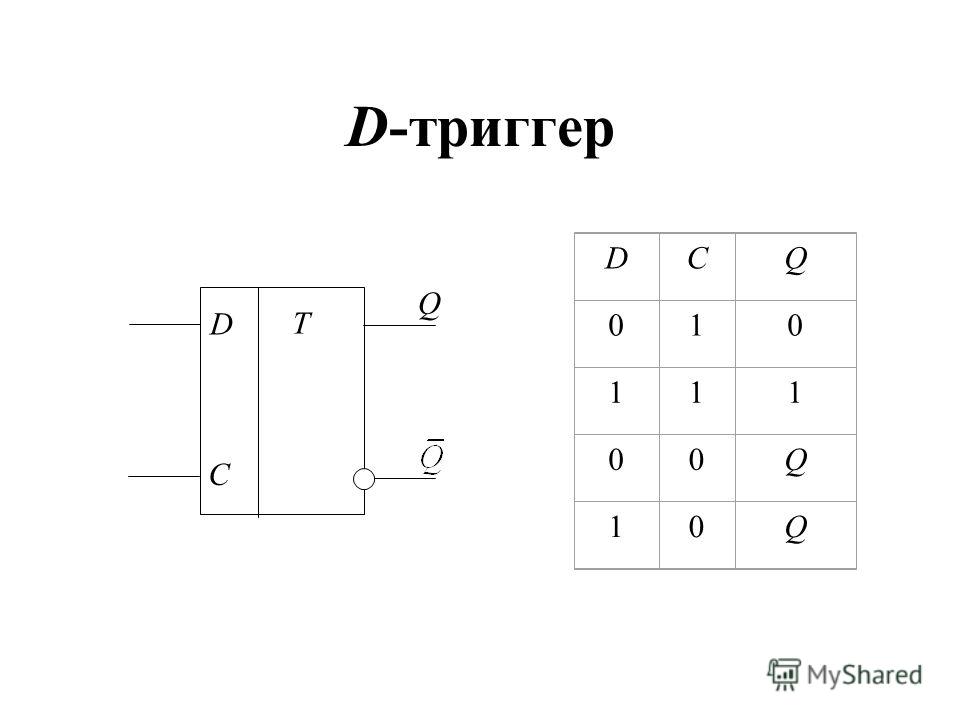

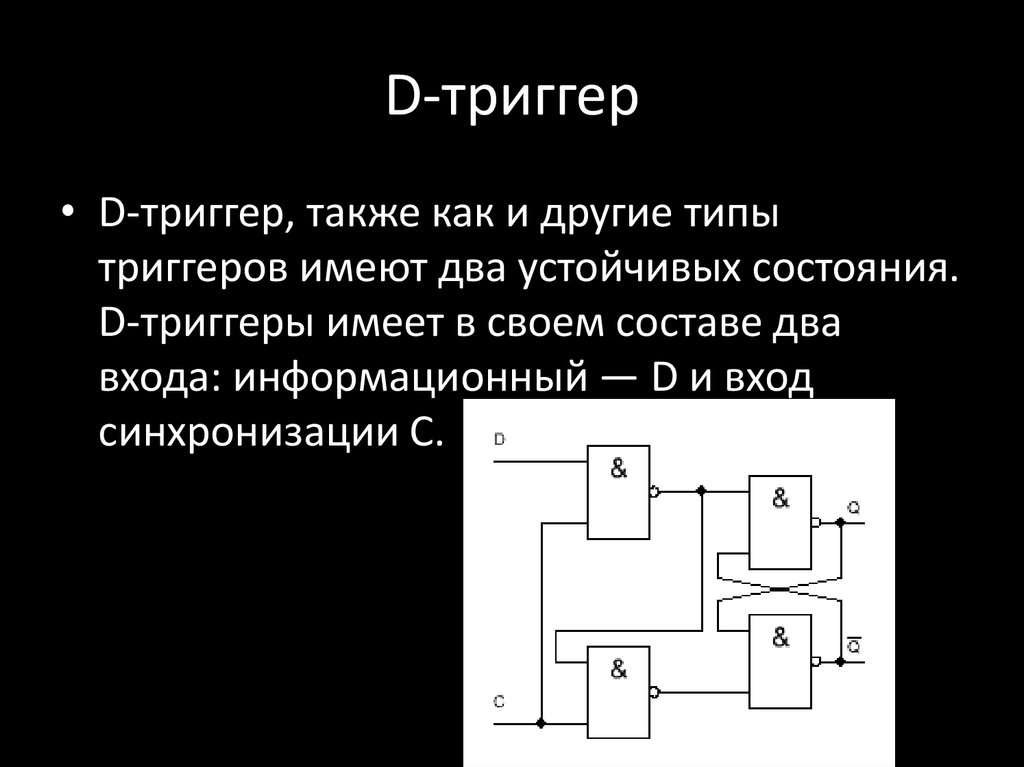

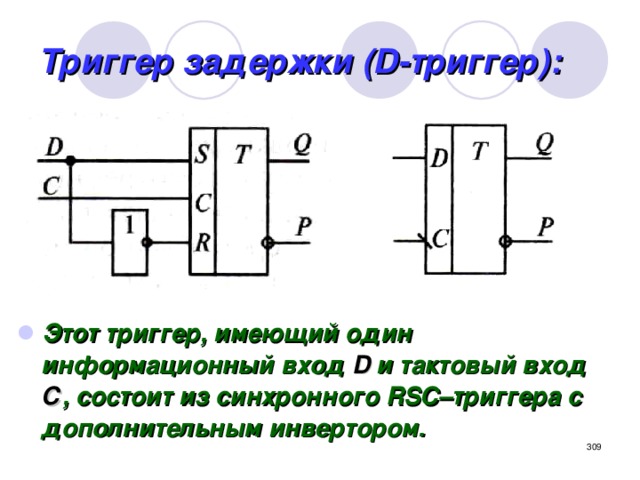

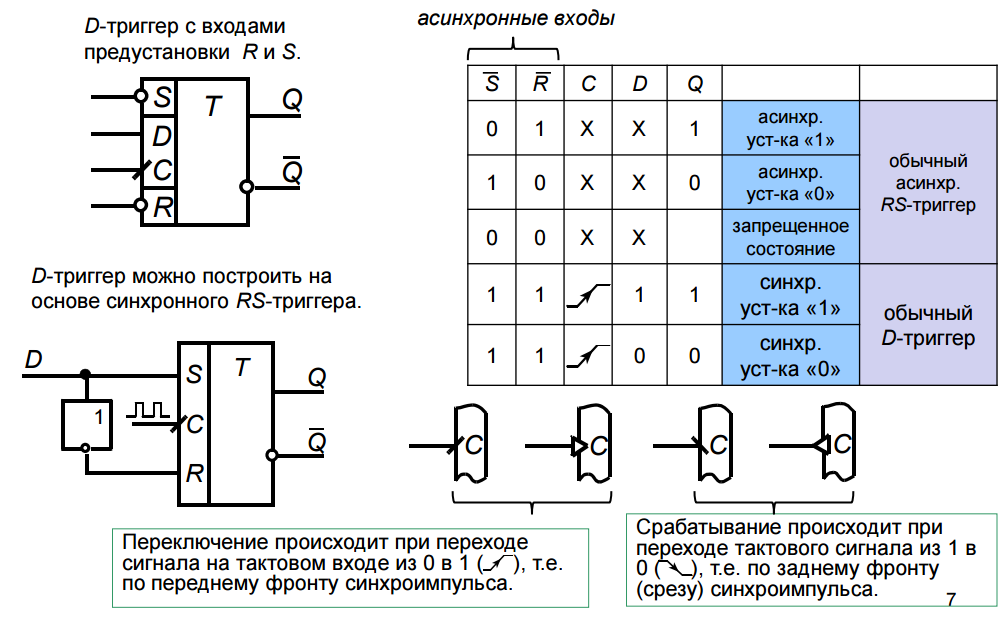

Триггер типа D (от слова delay – задержка)

принимает информацию по одному входу и реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый

D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

Синхронизируемы однотактный D-триггер задерживает рапространение входного

сигнала на время паузы между синхросигналами (задержка на полпериода). Для

задержки на период (на один такт) используется двухтактный D-триггер.

D-триггер имеет только режимы установки 1 и 0. В связи с этим несинхронизируемый

D-триггер не применяется, т.к. его выход будет просто повторять входной сигнал.

Синхронизируемы однотактный D-триггер задерживает рапространение входного

сигнала на время паузы между синхросигналами (задержка на полпериода). Для

задержки на период (на один такт) используется двухтактный D-триггер.

|

Inputs |

Outputs | |||||

|

D |

C |

S |

R |

Q |

Q^ |

|

|

X |

X |

1 |

0 |

0 |

1 | |

|

X |

X |

0 |

1 |

1 |

0 | |

|

X |

X |

0 |

0 |

1 |

0 | |

|

X |

0 |

1 |

1 |

Q’ |

QB’ | |

|

X |

1 |

1 |

1 |

Q’ |

QB’ | |

|

0 |

RE |

1 |

1 |

0 |

1 | |

|

1 |

RE |

1 |

1 |

1 |

0 | |

Таблица 3. —

инверсный информационный выход

—

инверсный информационный выход

Параметры S и

R служат для задания начальных условий

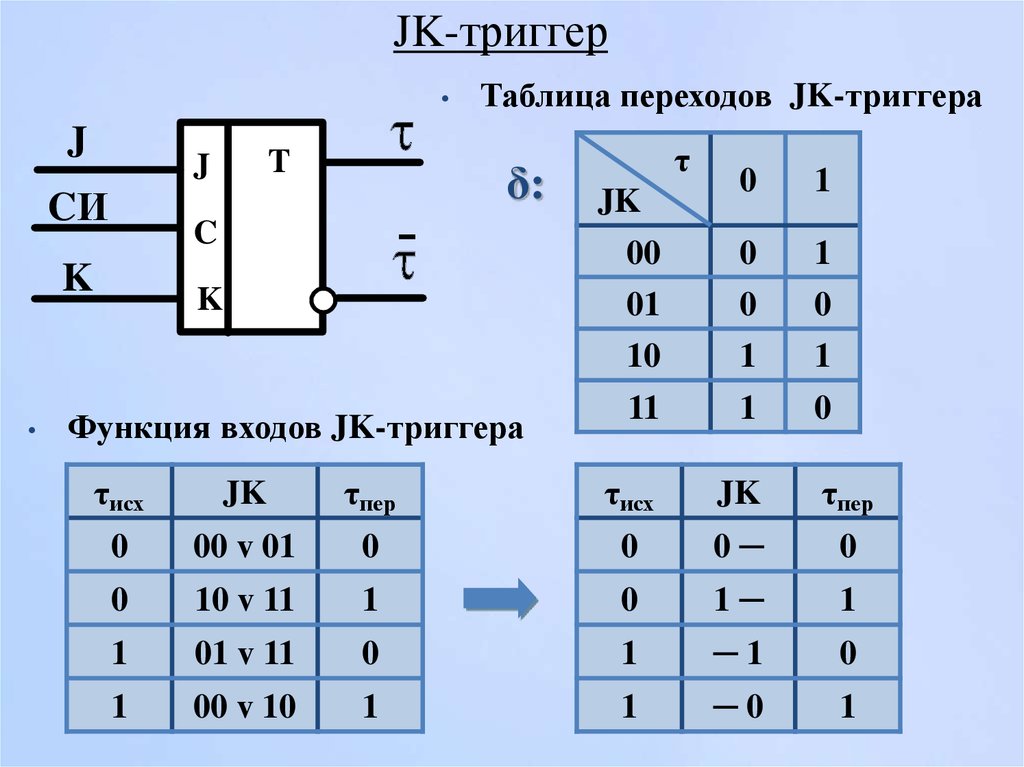

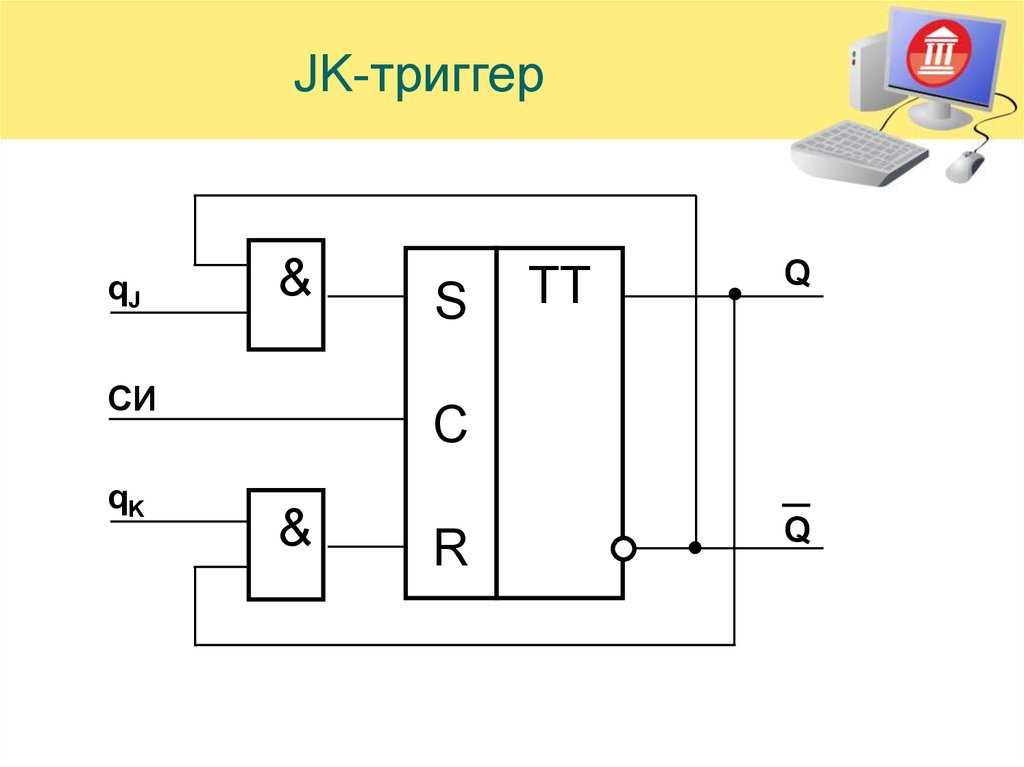

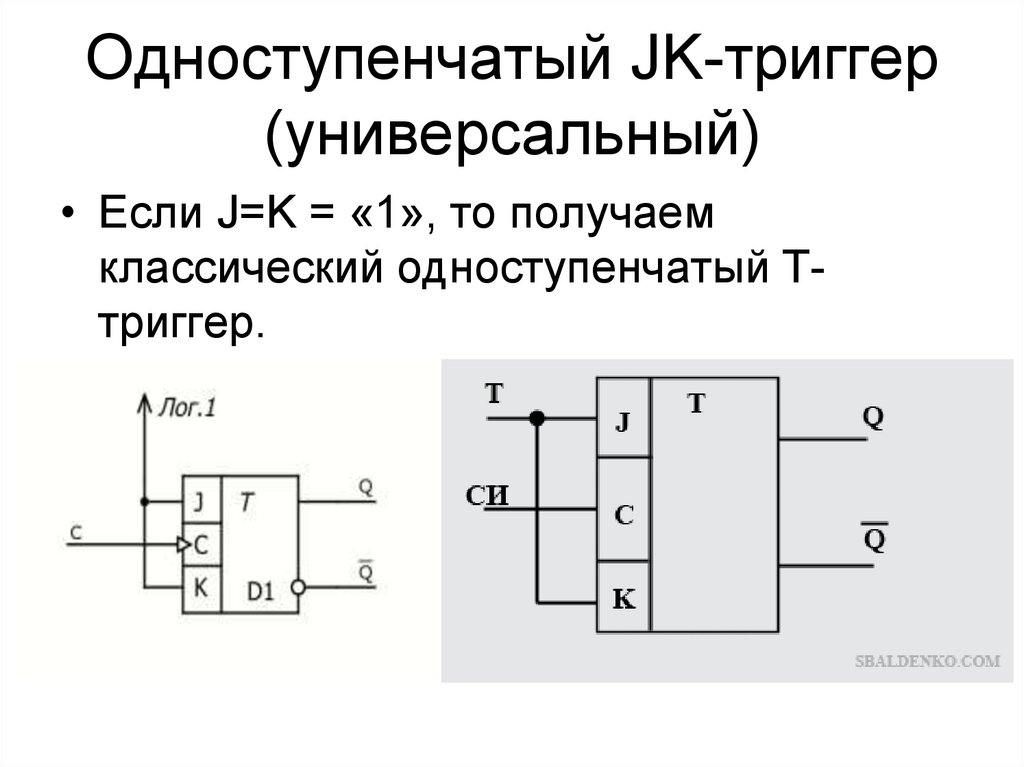

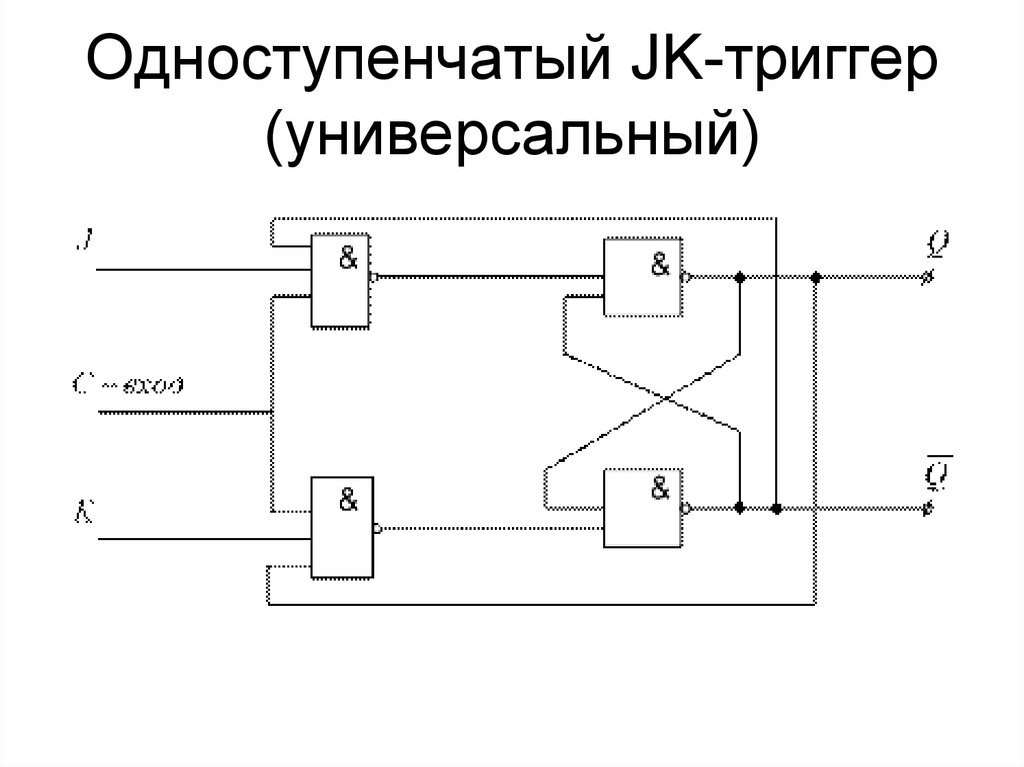

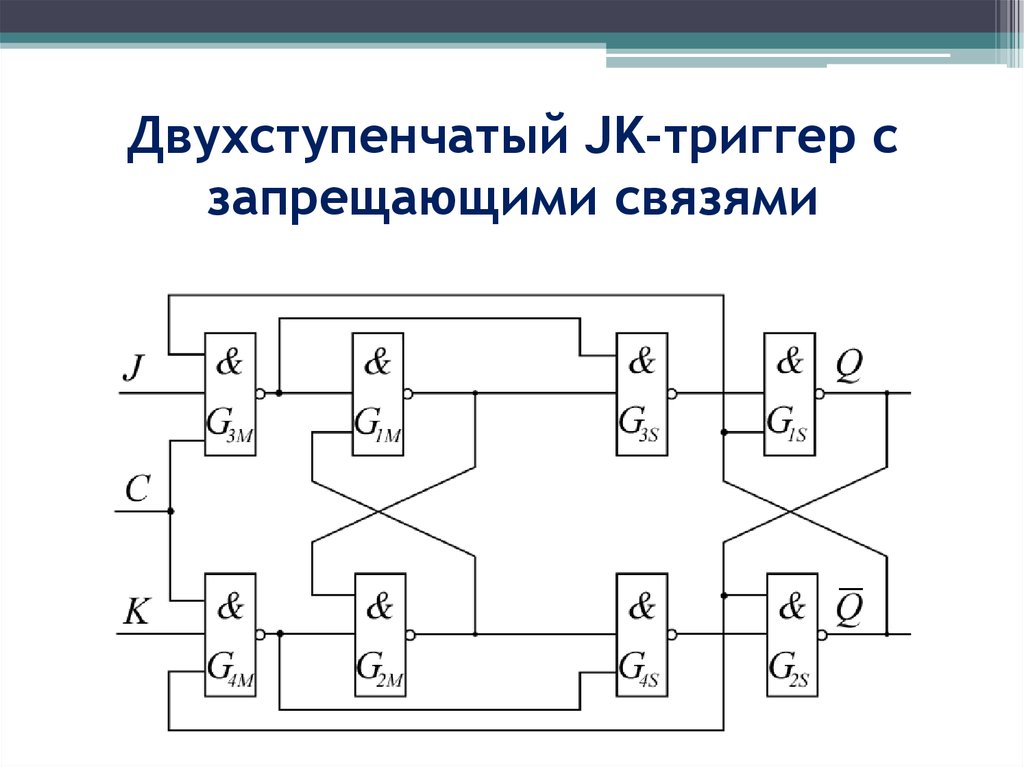

Триггер типа JK — универсален, с раздельной установкой нулевого и единичного состояния, в зависимости от соединения его входов он может работать как RS, T, D триггера. В отличие от триггера типа RS в нем не запрещена одновременная подача сигналов на оба входа. Входы J и K эквивалентны входам S и R установки триггера соответственно в состояния “1” и “0”.При объединении входов J и K и при подаче на них счетных импульсов.Вход J при раздельном использовании входов играет роль входа установки в единицу, а вход K — роль входа установки в нуль.

Рисунок 3.3.1.9 — Условное обозначение JK-триггера

Параметры синхронного JK-триггера:

C

— синхронизирующий входJ и K — информационные входы триггера

S — установка 1

R — установка 0

Q — информационный выход

Q^ — инверсный информационный выход

Параметры S и R служат для задания начальных условий (см.

X

X

X

1

0

0

1

X

X

X

0

1

1

0

X

X

X

0

0

1

0

X

X

0

1

1

Q’

QB’

X

X

1

1

1

Q’

QB’

0

0

FE

1

1

Q’

QB’

0

1

FE

1

1

0

1

1

0

FE

1

1

1

0

1

1

FE

1

1

QB’

Q’

Таблица 3. 3.1.5 — Таблица

истинности синхронного JK-триггера

3.1.5 — Таблица

истинности синхронного JK-триггера

Триггер типа T называется триггером со счетным входом (или счетным триггером). Он изменяет свое состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал. Обозначение триггера пришло от первой буквы анг.слова toggle-защелка.

Т.к. в Electronics Workbench не приводится T-триггер его можно получить объединив информационные входы JK-триггера.

Задание:

— схемы триггеров;

— временные диаграммы работы триггеров.

Задания выполняются соответственно по вариантам:

- Схема двухтактного RS-триггера на базе элементов ИЛИ-НЕ;

- Схема двухтактного RS-триггера с использованием микросхемы приведенной Electronics Workbench;

- Схема D -триггера с использованием микросхемы приведенной в Electronics Workbench;

- Схема JK-триггера с использованием микросхемы приведенной в Electronics Workbench;

- Схема T-триггера с использованием микросхемы приведенной в Electronics Workbench.

Примечание: Для построения и анализа работы T, D и JK триггеров используйте их условные обозначения.

BFSIII AR C1 | AR 15 Триггер

Распродажа

|

429,99 долларов США $386,99

Не для гражданских продаж в: Калифорния, Коннектикут, округ Колумбия, Германия, Флорида, Гавайи, Айова, Мэриленд, Нью-Джерси, Нью-Йорк, Род-Айленд и Вашингтон

Количество:

Добавление в корзину… Товар добавлен

BFSIII® AR-C1 для платформы AR

Время тока: в складе

. ) представляет собой 3-позиционный спусковой крючок. В положении 3 он производит один выстрел при нажатии и один выстрел при отпускании, что делает этот спусковой крючок идеальным как для тактического использования, так и для соревнований. BFSIII® обеспечивает значительно меньшее время между раундами, что позволяет создавать более тесные группы.

) представляет собой 3-позиционный спусковой крючок. В положении 3 он производит один выстрел при нажатии и один выстрел при отпускании, что делает этот спусковой крючок идеальным как для тактического использования, так и для соревнований. BFSIII® обеспечивает значительно меньшее время между раундами, что позволяет создавать более тесные группы.

Работа спускового крючка:

Положение 1 — Безопасный — Не стреляет

Положение 2 — Полуавтоматическое — Стреляет 1 выстрел за одно нажатие

ХАРАКТЕРИСТИКИ:* Раунд запуска можно отменить, просто переведя наш запатентованный селектор из режима Binary®, удерживая курок нажатым

* Простота установки

* Плавное нажатие на спусковой крючок: 4,5 фунта, +/- 0,5 фунта

* Положительный сброс в фазе спуска

* Усиленные буферные пружины для оптимальной гибкости NATO, 308 Win, 300 BLK, 9 мм, Rimfire и т. д….

д….

* Совместимость с большинством болтовых держателей (BCG)

* Идеально подходит для стрелков-соревнователей, тактических стрелков и любителей активного отдыха

* AR-C1 поставляется со стандартным изогнутым спусковым крючком.

- Не для гражданских продаж в:

- Калифорния, Коннектикут, округ Колумбия, Флорида, Гавайи, Айова, Мэриленд, Нью-Джерси, Нью-Йорк, Род-Айленд и Вашингтон

- Триггер для:

- Огнестрельное оружие на платформе AR

- Профиль триггера:

- Изогнутый

Часто задаваемые вопросы — Schneider Electric

{"searchBar":{"inputPlaceholder":"Поиск по ключевому слову или задать вопрос","searchBtn":"Поиск","error":"Пожалуйста, введите ключевое слово для поиска"}} 0.0.0″> Что заставляет ATV320 отображать ошибку OBF?Проблема: Ошибка OBF на ATV320 Линейка продуктов: Altivar 320 Окружающая среда: Все Причина: Ошибка OBF на дисплее привода Устранение: Возможные причины: • Слишком резкое торможение или тяговая нагрузка. • Слишком высокое напряжение питания….

В чем основные отличия контакторов LC1D и LC1K?

Выпуск: Различия между контакторами LC1D и LC1K Линейка продуктов: Контакторы и пускатели IEC Окружающая среда: Контакторы Tesys K и Tesys D Разрешение: Контакторы D-Line крупнее, надежнее и…

Можно ли использовать пускатели GV2, GV3 и GV7 с обратной подачей?

6.2.1″> Проблема: Обратная подача Линейка продуктов GV2, GV3 и GV7: Пускатели и устройства защиты двигателей Окружающая среда: Ручные пускатели PowerPact™ Решение: Не рекомендуется.

Как сохранить параметры в клавиатуре и загрузить на другой идентичный…

Проблема: Попытка сохранить параметры в клавиатуре и загрузите их в другой идентичный привод ATV630. Линейка продуктов: Приводы ATV630 Среда: Клавиатура Причина: Передача файлов Решение: Перейти к главному…

Часто задаваемые вопросы о популярных видеоПопулярные видео

Видео: Как подключить TeSys T к Somove через Modbus. ..

..

Преобразование проекта ProWORX 32 в Unity Pro

Видео: Как подключить и запрограммировать привод ATV61/71 для 3-проводного подключения…

Узнайте больше в разделе часто задаваемых вопросов по общим знаниямОбщие знания

Проверка сопротивления изоляции и влажности

Проблема: Как влажность влияет на результаты испытаний сопротивления изоляции? Линейка продуктов: автоматические выключатели Окружающая среда: выключатели в литом и изолированном корпусах Разрешение: высокая влажность может значительно…

В чем разница между PNP и NPN при описании 3-проводных… , емкостные, ультразвуковые и фотоэлектрические) являются твердотельными. Термин твердотельный относится к типу компонентов, используемых в датчике.

3.40. Двухтактный T-триггер

(слева) и его временные диаграммы

(справа)

3.40. Двухтактный T-триггер

(слева) и его временные диаграммы

(справа)